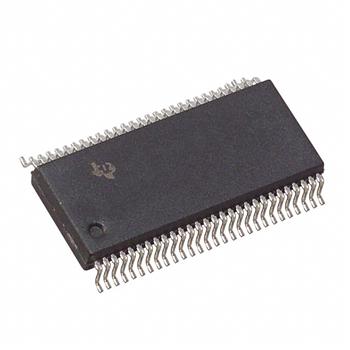

- 封装:56-BSSOP(0.295",7.50mm 宽)

- RoHS:无铅 / 符合限制有害物质指令(RoHS)规范要求

- 包装方式:Digi-Reel®

- 参考价格:$4.0185-$6.77

更新日期:2024-04-01 00:04:00

产品简介:具有三态输出的 18 位通用总线收发器

查看详情- 封装:56-BSSOP(0.295",7.50mm 宽)

- RoHS:无铅 / 符合限制有害物质指令(RoHS)规范要求

- 包装方式:Digi-Reel®

- 参考价格:$4.0185-$6.77

SN74ABT162601DLR 供应商

- 公司

- 型号

- 品牌

- 封装/批号

- 数量

- 地区

- 日期

- 说明

- 询价

-

TI

-

原厂原装

22+ -

3288

-

上海市

-

-

-

一级代理原装

-

TEXAS

-

-

0 -

19492

-

杭州

-

-

-

原装正品现货

-

-

2019+ -

5800

-

上海市

-

-

-

全新原装现货

-

TI(德州仪器)

-

SSOP-56

2022+ -

12000

-

上海市

-

-

-

原装可开发票

-

TI

-

SSOP

21+ -

992

-

上海市

-

-

-

原装现货,品质为先!请来电垂询!

-

TI

-

SSOP56

23+ -

5800

-

上海市

-

-

-

进口原装现货,杜绝假货。

SN74ABT162601DLR 中文资料属性参数

- 标准包装:1

- 类别:集成电路 (IC)

- 家庭:逻辑 - 通用总线函数

- 系列:74ABT

- 逻辑类型:通用总线收发器

- 输入数:-

- 电路数:18 位

- 输出电流高,低:32mA,64mA; 12mA,12mA

- 电源电压:4.5 V ~ 5.5 V

- 工作温度:-40°C ~ 85°C

- 安装类型:表面贴装

- 封装/外壳:56-BSSOP(0.295",7.50mm 宽)

- 供应商设备封装:56-SSOP

- 包装:®

- 其它名称:296-1028-6

产品特性

- Members of the Texas Instruments WidebusTM Family

- B-Port Outputs Have Equivalent 25- Series Resistors, So No External Resistors Are Required

- State-of-the-Art EPIC-II BTM BiCMOS Design Significantly Reduces Power Dissipation

- UBTTM (Universal Bus Transceiver) Combines D-Type Latches and D-Type Flip-Flops for Operation in Transparent, Latched, Clocked, or Clock-Enabled Mode

- Latch-Up Performance Exceeds 500 mA Per JESD 17

- Typical VOLP (Output Ground Bounce) < 0.8 V at VCC = 5 V, TA = 25°C

- High-Impedance State During Power Up and Power Down

- Flow-Through Architecture Optimizes PCB Layout

- Package Options Include Plastic 300-mil Shrink Small-Outline (DL) and Thin Shrink Small-Outline (DGG) Packages and 380-mil Fine-Pitch Ceramic Flat (WD) Package Using 25-mil Center-to-Center Spacings Widebus, EPIC-IIB, and UBT are trademarks of Texas Instruments Incorporated.

产品概述

These 18-bit universal bus transceivers combine D-type latches and D-type flip-flops to allow data flow in transparent, latched, and clocked modes.

Data flow in each direction is controlled by output-enable (OEAB\ and OEBA\), latch-enable (LEAB and LEBA), and clock (CLKAB and CLKBA) inputs. The clock can be controlled by the clock-enable (CLKENAB\ and CLKENBA\) inputs.

For A-to-B data flow, the device operates in the transparent mode when LEAB is high. When LEAB is low, the A data is latched if CLKAB is held at a high or low logic level. If LEAB is low, the A data is stored in the latch/flip-flop on the low-to-high transition of CLKAB. Output-enable OEAB\ is active-low. When OEAB\ is low, the outputs are active. When OEAB\ is high, the outputs are in the high-impedance state. Data flow for B to A is similar to that of A to B but uses OEBA\, LEBA, CLKBA, and CLKENBA\.

The B-port outputs, which are designed to source or sink up to 12 mA, include equivalent 25-

series resistors to reduce overshoot and undershoot.

When VCC is between 0 and 2.1 V, the device is in the high-impedance state during power up or power down. However, to ensure the high-impedance state above 2.1 V, OE\ should be tied to VCC through a pullup resistor; the minimum value of the resistor is determined by the current-sinking capability of the driver.

The SN54ABT162601 is characterized for operation over the full military temperature range of -55°C to 125°C. The SN74ABT162601 is characterized for operation from -40°C to 85°C.

SN74ABT162601DLR 数据手册

| 数据手册 | 说明 | 数量 | 操作 |

|---|---|---|---|

SN74ABT162601DLR SN74ABT162601DLR

|

Universal Bus Transceiver 18-Bit 56-SSOP |

16页,1.01M | 查看 |

SN74ABT162601DLR 相关产品

- 74ALVCH16501DGGRG4

- 74LVTH16501DGGRE4

- CD74HC299E

- CD74HC299M96

- CD74HCT299E

- CD74HCT299M96

- CVMEH22501AIDGGREP

- CVMEH22501AIDGVREP

- GTLP18T612MTDX

- SN74ABT162500DL

- SN74ABT162601DGGR

- SN74ABT16500BDGGR

- SN74ABT16500BDL

- SN74ABT16500BDLR

- SN74ABT16501DGGR

- SN74ABT16501DL

- SN74ABT16501DLR

- SN74ABT16601DGGR

- SN74ABT16601DL

- SN74ABT16601DLR

- SN74ABTH182502APM

- SN74ABTH182504APM

- SN74ABTH18502APM

- SN74ABTH18502APMR

- SN74ABTH18504APM

- SN74ABTH32316PN

- SN74ABTH32318PN

- SN74ALVC162334DGGR

- SN74ALVC162334DGVR

- SN74ALVC162334DLR

搜索

搜索

发布采购

发布采购