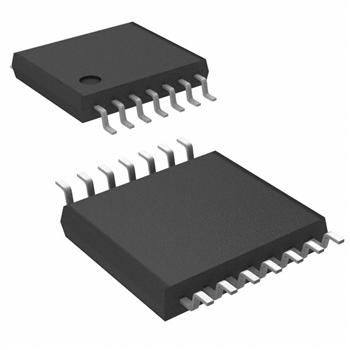

- 封装:14-TSSOP(0.173",4.40mm 宽)

- RoHS:无铅 / 符合限制有害物质指令(RoHS)规范要求

- 包装方式:管件

- 参考价格:$0.6875-$1.71

更新日期:2024-04-01 00:04:00

产品简介:具有总线保持、TTL 兼容型 CMOS 输入和三态输出的 4 通道、2.7V 至 3.6V 缓冲器

查看详情- 封装:14-TSSOP(0.173",4.40mm 宽)

- RoHS:无铅 / 符合限制有害物质指令(RoHS)规范要求

- 包装方式:管件

- 参考价格:$0.6875-$1.71

SN74LVT125PW 供应商

- 公司

- 型号

- 品牌

- 封装/批号

- 数量

- 地区

- 日期

- 说明

- 询价

-

SN74LVT125PWR

原装现货 -

TI

-

TSSOP14

2024+ -

640

-

北京市

-

03-11

-

原装现货北京库存

-

TI

-

原厂原装

22+ -

3288

-

上海市

-

-

-

一级代理原装

-

TI

-

TSSOP

23+ -

46000

-

合肥

-

-

-

科大讯飞战略投资企业,提供一站式配套服务

-

TI

-

TSSOP16

23+ -

15000

-

上海市

-

-

-

中国区代理原装现货热卖特价

-

TI(德州仪器)

-

TSSOP-14

2022+ -

12000

-

上海市

-

-

-

原装可开发票

-

TI

-

TSSOP-14/超薄

- -

195

-

上海市

-

-

-

经营22年实体店原装,具体年份和数量以实际为准

-

TI

-

-

2019+ -

5800

-

上海市

-

-

-

全新原装现货

-

TI

-

14-TSSOP

新批号 -

887000

-

上海市

-

-

-

原厂发货进口原装微信同步QQ893727827

SN74LVT125PW 中文资料属性参数

- 标准包装:90

- 类别:集成电路 (IC)

- 家庭:逻辑 - 缓冲器,驱动器,接收器,收发器

- 系列:74LVT

- 逻辑类型:缓冲器/线路驱动器,非反相

- 元件数:4

- 每个元件的位元数:1

- 输出电流高,低:32mA,64mA

- 电源电压:2.7 V ~ 3.6 V

- 工作温度:-40°C ~ 85°C

- 安装类型:表面贴装

- 封装/外壳:14-TSSOP(0.173",4.40mm 宽)

- 供应商设备封装:14-TSSOP

- 包装:管件

- 其它名称:296-34082-5SN74LVT125PW-ND

产品特性

- Supports Mixed-Mode Signal Operation (5-V Input and Output Voltages With 3.3-V VCC)

- Supports Unregulated Battery Operation Down to 2.7 V

- Typical VOLP (Output Ground Bounce) <0.8 V at VCC = 3.3 V, TA = 25°C

- Ioff Supports Partial-Power-Down Mode Operation

- Bus-Hold Data Inputs Eliminate the Need for External Pullup Resistors

- Latch-Up Performance Exceeds 500 mA Per JEDEC Standard JESD-17

- ESD Protection Exceeds JESD 22 2000-V Human-Body Model (A114-A) 200-V Machine Model (A115-A)

- 2000-V Human-Body Model (A114-A)

- 200-V Machine Model (A115-A)

产品概述

This bus buffer is designed specifically for low-voltage (3.3-V) VCC operation, but with the capability

to provide a TTL interface to a 5-V system environment.The SN74LVT125 features independent line drivers with 3-state outputs. Each output is in the high-impedance state

when the associated output-enable (OE)\ input is high.Active bus-hold circuitry holds unused or undriven inputs at a valid logic state. Use of pullup or pulldown resistors

with the bus-hold circuitry is not recommended.This device is fully specified for partial-power-down applications using Ioff. The Ioff

circuitry disables the outputs, preventing damaging current backflow through the device when it is powered down.To ensure the high-impedance state during power up or power down, OE\ should be tied to VCC through a

pullup resistor; the minimum value of the resistor is determined by the current-sinking capability of the driver.

SN74LVT125PW 数据手册

| 数据手册 | 说明 | 数量 | 操作 |

|---|---|---|---|

SN74LVT125PW SN74LVT125PW

|

3.3-V ABT QUADRUPLE BUS BUFFERS WITH 3-STATE OUTPUTS |

7 Pages页,118K | 查看 |

SN74LVT125PW SN74LVT125PW

|

Buffer, Non-Inverting 4 Element 1 Bit per Element Push-Pull Output 14-TSSOP |

16页,678K | 查看 |

SN74LVT125PW 相关产品

- 100314QC

- 1P1G125QDCKRG4Q1

- 1P1G125QDCKRQ1

- 1P1G126QDBVRQ1

- 74ABT125PW,118

- 74ABT162244CSSX

- 74ABT162244DGGRG4

- 74ABT162245DLRG4

- 74ABT16245ADGGRG4

- 74ABT244D,623

- 74ABT245PW,118

- 74AC11244DBR

- 74AC11244DWR

- 74AC11244PWR

- 74AC11245DW

- 74AC11245DWR

- 74AC16244DGGR

- 74AC16244DL

- 74AC16244DLR

- 74AC16245DLR

- 74AC16652DL

- 74ACT11244DBR

- 74ACT11244DWR

- 74ACT11244PWR

- 74ACT11245DBR

- 74ACT11245DWR

- 74ACT11245NSR

- 74ACT11245PWR

- 74ACT16244DGGR

- 74ACT16244DLR

搜索

搜索

发布采购

发布采购