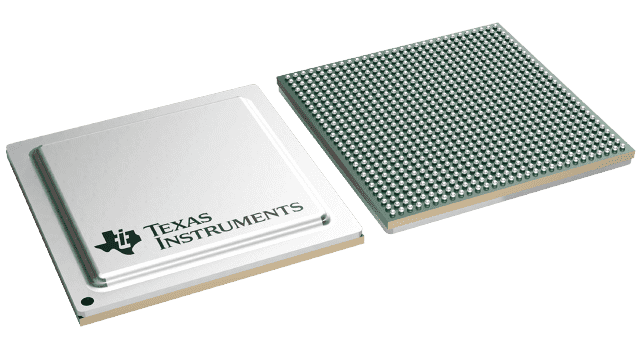

- 封装:841-BFBGA,FCBGA

- RoHS:无铅 / 符合限制有害物质指令(RoHS)规范要求

- 包装方式:托盘

- 参考价格:$230.4-$278.4

更新日期:2024-04-01 00:04:00

产品简介:用于通信和电信的 4 核定点和浮点 DSP

查看详情- 封装:841-BFBGA,FCBGA

- RoHS:无铅 / 符合限制有害物质指令(RoHS)规范要求

- 包装方式:托盘

- 参考价格:$230.4-$278.4

TMS320C6670ACYP2 供应商

- 公司

- 型号

- 品牌

- 封装/批号

- 数量

- 地区

- 日期

- 说明

- 询价

-

TI

-

原厂原装

22+ -

3288

-

上海市

-

-

-

一级代理原装

-

TI

-

原厂原装

2318+ -

9200

-

合肥

-

-

-

科大讯飞战略投资企业

TMS320C6670ACYP2 中文资料属性参数

- 标准包装:44

- 类别:集成电路 (IC)

- 家庭:嵌入式 - DSP(数字式信号处理器)

- 系列:TMS320C66x

- 类型:定点/浮点

- 接口:EBI/EMI,以太网 MAC,PCIe,I²C,SPI,SRIO,UART

- 时钟速率:1.2GHz

- 非易失内存:ROM(128 kB)

- 芯片上RAM:6.25MB

- 电压 - 输入/输出:1.0V,1.5V,1.8V

- 电压 - 核心:1.00V

- 工作温度:0°C ~ 100°C

- 安装类型:表面贴装

- 封装/外壳:841-BFBGA,FCBGA

- 供应商设备封装:841-FCBGA(24x24)

- 包装:托盘

- 其它名称:296-30468-5

产品特性

- Four TMS320C66x DSP Core Subsystems at 1.00 GHz and 1.2GHz 153.6 GMAC/76.8 GFLOP @ 1.2GHz 32KB L1P, 32KB L1D, 1024KB L2 Per Core 2MB Shared L2

- 153.6 GMAC/76.8 GFLOP @ 1.2GHz

- 32KB L1P, 32KB L1D, 1024KB L2 Per Core

- 2MB Shared L2

- Multicore Navigator and TeraNet Switch Fabric - 2 Tb

- Network Coprocessors- Packet Accelerator, Security Accelerator

- Four Lanes of SRIO 2.1 - 5 Gbaud Per Lane Full Duplex

- Two Lanes PCIe Gen2 - 5 Gbaud Per Lane Full Duplex

- HyperLink - 50Gbaud Operation, Full Duplex

- Ethernet MAC Subsystem - Two SGMII Ports w/ 10/100/1000 Mbps operation

- 64-Bit DDR3 Interface (DDR3-1600) - 8 GByte Addressable Memory Space

- Six Lane SerDes-Based Antenna Interface (AIF2) - Operating at up to 6.144 Gbps

- Hardware Coprocessors -Enhanced Coprocessor for Turbo Encoding -Three Enhanced Coprocessors for Turbo Decoding -Four Viterbi Decoders -Three Fast Fourier Transform Coprocessors -Bit Rate CoProcessor -Two Receiver Accelerators for WCDMA -Transmitt Accelerator for WCDMA

- -Enhanced Coprocessor for Turbo Encoding -Three Enhanced Coprocessors for Turbo Decoding -Four Viterbi Decoders -Three Fast Fourier Transform Coprocessors -Bit Rate CoProcessor -Two Receiver Accelerators for WCDMA -Transmitt Accelerator for WCDMA

- Four Rake Search Accelerators for Chip Rate Processing and Reed-Muller Decoding

- I2C Interface, 16 GPIO Pins, SPI Interface

- Eight 64-Bit Timers, Three On-Chip PLLs

产品概述

The TMS320C6670 Multicore Fixed and Floating Point System on Chip is a member of the C66xx SoC family based on TI's new KeyStone Multicore SoC Architecture designed specifically for high performance applications such as software defined radio, emerging broadband and other communications segments. Integrated with four C66x CorePac DSPs, each core runs at 1.0 to 1.20 GHz enabling up to 4.8 GHz. Hardware acceleration provides a highly integrated, power efficient and easy to use platform for implementing a combination of multi-band, multi-standard waveforms, including proprietary air-interfaces. The C6670 platform is power efficient and easy to use. The C66x CorePac DSP is fully backward compatible with all existing C6000 family of fixed and floating point DSPs.

TMS320C6670ACYP2 电路图

TMS320C6670ACYP2 电路图

TMS320C6670ACYP2 相关产品

- ADSP-2104BPZ-80

- ADSP-2105BPZ-80

- ADSP-21060CZ-160

- ADSP-21060KBZ-160

- ADSP-21060KSZ-133

- ADSP-21060LABZ-160

- ADSP-21060LCB-133

- ADSP-21060LCW-160

- ADSP-21060LKSZ-133

- ADSP-21061LASZ-176

- ADSP-21061LKSZ-176

- ADSP-21062KBZ-160

- ADSP-21062KSZ-160

- ADSP-21062LCSZ-160

- ADSP-21062LKBZ-160

- ADSP-21065LCCAZ240

- ADSP-21065LKCAZ264

- ADSP-21160NCB-100

- ADSP-21160NCBZ-100

- ADSP-21160NKBZ-100

- ADSP-21161NKCAZ100

- ADSP-21261SKSTZ150

- ADSP-21262SBBC-150

- ADSP-21262SBBCZ150

- ADSP-21266SKBCZ-2D

- ADSP-21266SKSTZ-1D

- ADSP-21266SKSTZ-2D

- ADSP-21362BSWZ-1AA

- ADSP-21363BBC-1AA

- ADSP-21363YSWZ-2AA

搜索

搜索

发布采购

发布采购