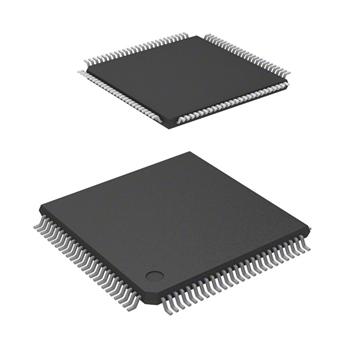

A3P125-VQG100

嵌入式 - FPGA(现场可编程门阵列)- 封装:100-TQFP

- RoHS:无铅 / 符合限制有害物质指令(RoHS)规范要求

- 参考价格:$10.71-$9.765

更新日期:2024-04-01 00:04:00

A3P125-VQG100

嵌入式 - FPGA(现场可编程门阵列)产品简介:IC FPGA 1024MAC 133I/O 100VQFP

- 封装:100-TQFP

- RoHS:无铅 / 符合限制有害物质指令(RoHS)规范要求

- 参考价格:$10.71-$9.765

A3P125-VQG100 供应商

- 公司

- 型号

- 品牌

- 封装/批号

- 数量

- 地区

- 日期

- 说明

- 询价

-

Microchip

-

TQFP

23+ -

800

-

上海市

-

-

-

全新原厂原装上海仓现货

-

MICROCHIP

-

SMD

23+ -

5000

-

上海市

-

-

-

原装进口

-

Actel

-

QFP

7 -

1000

-

杭州

-

-

-

原装正品现货

-

ACTEL

-

TQFP

23+ -

58000

-

上海市

-

-

-

进口原装现货,杜绝假货。

-

TSSOP

23+ -

46000

-

合肥

-

-

-

科大讯飞战略投资企业,提供一站式配套服务

-

Actel

-

TQFP-100

新批号 -

887000

-

上海市

-

-

-

原厂直发进口原装微信同步QQ893727827

A3P125-VQG100 中文资料属性参数

- 标准包装:90

- 类别:集成电路 (IC)

- 家庭:嵌入式 - FPGA(现场可编程门阵列)

- 系列:ProASIC3

- LAB/CLB数:-

- 逻辑元件/单元数:-

- RAM 位总计:36864

- 输入/输出数:71

- 门数:125000

- 电源电压:1.425 V ~ 1.575 V

- 安装类型:表面贴装

- 工作温度:0°C ~ 70°C

- 封装/外壳:100-TQFP

- 供应商设备封装:100-VQFP(14x14)

- 其它名称:1100-1025

A3P125-VQG100 数据手册

| 数据手册 | 说明 | 数量 | 操作 |

|---|---|---|---|

A3P125-VQG100I A3P125-VQG100I

|

March 2016 I ? 2016 Microsemi Corporation ProASIC3 Flash Family FPGAs with Optional Soft ARM Support Features and Benefits High Capacity ? 15 K to 1 M System Gates ? Up to 144 Kbits of True Dual-Port SRAM ? Up to 300 User I/Os Reprogrammable Flash Technology ? 130-nm, 7-Layer Metal (6 Copper), Flash-Based CMOS Process ? Instant On Level 0 Support ? Single-Chip Solution ? Retains Programmed Design when Powered Off High Performance ? 350 MHz System Performance ? 3.3 V, 66 MHz 64-Bit PCI ? In-System Programming (ISP) and Security ? ISP Using On-Chip 128-Bit Advanced Encryption Standard (AES) Decryption (except ARM ? -enabled ProASIC ? 3 devices) via JTAG (IEEE 1532–compliant) ? ? FlashLock ? to Secure FPGA Contents Low Power ? Core Voltage for Low Power ? Support for 1.5 V-Only Systems ? Low-Impedance Flash Switches High-Performance Routing Hierarchy ? Segmented, Hierarchical Routing and Clock Structure Advanced I/O ? 700 Mbps DDR, LVDS-Capable I/Os (A3P250 and above) ? 1.5 V, 1.8 V, |

221页,6.33M | 查看 |

A3P125-VQG100I_773 A3P125-VQG100I_773

|

March 2016 I ? 2016 Microsemi Corporation ProASIC3 Flash Family FPGAs with Optional Soft ARM Support Features and Benefits High Capacity ? 15 K to 1 M System Gates ? Up to 144 Kbits of True Dual-Port SRAM ? Up to 300 User I/Os Reprogrammable Flash Technology ? 130-nm, 7-Layer Metal (6 Copper), Flash-Based CMOS Process ? Instant On Level 0 Support ? Single-Chip Solution ? Retains Programmed Design when Powered Off High Performance ? 350 MHz System Performance ? 3.3 V, 66 MHz 64-Bit PCI ? In-System Programming (ISP) and Security ? ISP Using On-Chip 128-Bit Advanced Encryption Standard (AES) Decryption (except ARM ? -enabled ProASIC ? 3 devices) via JTAG (IEEE 1532–compliant) ? ? FlashLock ? to Secure FPGA Contents Low Power ? Core Voltage for Low Power ? Support for 1.5 V-Only Systems ? Low-Impedance Flash Switches High-Performance Routing Hierarchy ? Segmented, Hierarchical Routing and Clock Structure Advanced I/O ? 700 Mbps DDR, LVDS-Capable I/Os (A3P250 and above) ? 1.5 V, 1.8 V, |

221页,6.33M | 查看 |

A3P125-VQG100 相关产品

- 5CGXFC7D7F31C8NES

- A1010B-2PLG68C

- A1010B-PL68C

- A1020B-1CQ84C

- A1020B-2PL68C

- A1020B-PG84C

- A1020B-PL44C

- A1020B-PL68C

- A1020B-PL68I

- A3P060-VQG100I

- A3P125-TQG144

- A3P125-TQG144I

- A42MX09-PQ100

- A42MX16-FTQ176

- A42MX24-2PQ208

- A54SX08A-TQG144I

- A54SX16A-TQG144I

- APA075-TQG100I

- APA150-FG256

- APA300-BG456

- APA300-PQG208I

- APA450-FG484

- EP1AGX60EF1152C6N

- EP1AGX60EF1152I6N

- EP1AGX90EF1152C6

- EP1C12F324C6

- EP1C12F324C7

- EP1C12F324I7

- EP1C12Q240C6

- EP1C20F324C7

搜索

搜索

发布采购

发布采购